UNIVERSITY OF CRETE DEPARTMENT OF COMPUTER SCIENCE FACULTY OF SCIENCES AND ENGINEERING

### Transparent Spatial Sharing of Multiple and Heterogeneous Accelerators

by

#### Emmanouil Pavlidakis

B.Sc., School of Engineering, Department of Information and Communication Systems Engineering, University of Aegean, Greece, 2012

M.Sc., Computer Science, Vrije Universiteit Amsterdam, Netherlands, 2016

PhD Dissertation

Presented

in Partial Fulfillment

of the Requirements

for the Degree of

Doctor of Philosophy

Heraklion, January 2024

© Copyright 2024 by Emmanouil Pavlidakis

#### UNIVERSITY OF CRETE

#### DEPARTMENT OF COMPUTER SCIENCE

#### **Transparent Spatial Sharing of Multiple and Heterogeneous Accelerators**

PhD Dissertation Presented

by Emmanouil Pavlidakis

in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

**APPROVED BY:**

Author: Emmanouil Pavlidakis

Supervisor: Angelos Bilas, Professor, University of Crete

Committee Member: Manolis G.H. Katevenis, Professor, University of Crete

Committee Member: Polyvios Pratikakis, Associate Professor, University of Crete

**Committee Member:** Vassilis D. Papaefstathiou, Assistant Professor, University of Crete

Committee Member: Giorgos Vasiliadis, Assistant Professor, Hellenic Mediterranean University

Committee Member: Leonidas Kosmidis, Computer Sciences, Barcelona Supercomputing Center, Spain

Committee Member: Vasileios Karakostas, Assistant Professor, National and Kapodistrian University of Athens

Department Chairman: Antonis Argyros, Professor, University of Crete

Heraklion, January 2024

Dedicated to my wife Elina, and my son Ioannis.

### Acknowledgments

During this fantastic trip called PhD, I was fortunate to collaborate with amazing people. First of all, I am grateful to my supervisor Prof. Angelos Bilas. He gave me the space, the time, the resources, and most importantly the guidance to sharpen my technical skills as well as develop my research taste. He was constantly there to discuss my ideas and concerns, providing directions and invaluable advice on my research. His mentorship and his interdisciplinary approach were a source of inspiration during my PhD studies.

I am grateful to my thesis committee members Manolis G.H. Katevenis, Polyvios Pratikakis, Vassilis D. Papaefstathiou, Giorgos Vasiliadis, Leonidas Kosmidis, and Vasileios Karakostas for their feedback during my defense and for their comments that helped me prepare the final version of this thesis.

I want to thank every single co-author I had all these years: Stelios Mavridis, Antony Chazapis, Giorgos Vasiliadis, and Nikos Chrysos. We worked together, we got rejected together, and we resubmitted together. I really enjoyed working with all of you.

After spending more than seven years in the Computer Architecture and VLSI Systems (CARV) lab of the Institute of Computer Science (ICS) in Foundation for Research and Technology-Hellas (FORTH), I feel like I have found a second family there. I met and worked alongside great people in this lab, and I want to express my deepest gratitude to Iacovos G. Kolokasis, Yannis Sfakianakis, Nikos Papakonstantinou, Anastasios Papagiannis, Giwrgos Saloustros, Giorgos Xanthakis, Eleni Kanellou, Theocharis Vavouris, Christos Kozanitis, and all other past and present members of CARV for preserving the balance between work and real life, making the lab a fun place to be.

I sincerely thank Manos Pigounakis, Giannis Silignakis, Giannis Marinos, and all other friends for their support, love, tolerance, and all the great moments we have shared.

I am grateful to my wife Elina Kiaoulia, for her patience, continuous support, and en-

couragement during the period of my doctoral thesis research. Additionally, I would like to express my gratitude to my newborn son Ioannis who joined us when I was writing my dissertation, for giving me unlimited happiness and pleasure.

Last but not least, I would like to express my deepest and most sincere gratitude to my parents, Ioannis and Maria, and my brother Vasilis for their love and support throughout all these years. Without your support I would have never been able to complete the dissertation.

I would also like to thank the Institute of Computer Science (ICS) in Foundation for Research and Technology-Hellas (FORTH), which supported me with graduate scholarships throughout my doctoral studies. Funding comes from several European projects that include: Vineyard (GA 687628), EVOLVE (GA 825061), EUPILOT (GA 101034126), DEEP-SEA (GA 955606), and HiPEAC (GA 871174).

### Abstract

Today, effectively utilizing multiple heterogeneous accelerators within applications and high-level Machine Learning (ML) frameworks like TensorFlow, PyTorch, and Caffe presents notable challenges across four key aspects: (a) sharing heterogeneous accelerators, (b) allocating available resources elastically during application execution, (c) providing the required performance for latency critical tasks, and (d) protecting application's data under spatial sharing.

In this dissertation, we introduce a novel runtime system designed to decouple applications from the intricacies of heterogeneous accelerators within a single server. Our approach entails a client-side API that allows applications to be written once without considering any low-level details, such as the number or type of accelerators. By leveraging our system, applications are liberated from the burdens of accelerator selection, memory allocations, and memory management operations. A backend service seamlessly manages these intricate tasks—referred to as the server—which is shared among all applications and boasts four primary features.

First, the server defers the assignment of a task to an accelerator until the latest feasible moment, setting it apart from current methods that allocate an application to an accelerator during its initialization phase. Subsequent to the task assignment decision but just prior to task execution, the server promptly transfers the necessary data to the designated accelerator. This dynamic task assignment and the lazy data placement enable adaptation to application load changes.

Second, to ensure that latency-critical GPU applications will have the desired performance under time-sharing, the server revokes the execution of long-running kernels. Our revocation mechanism stops a task by prematurely terminating the ongoing GPU kernel without preserving any state and replays it later. The server uses a runtime scheduler that prioritizes latency-critical tasks over batch and instructs the revocation mechanism when to kill a running kernel.

Third, to facilitate spatial accelerator sharing across applications, the server establishes multiple streams for GPUs and command queues for FPGAs. Regarding FPGAs, the server loads multi-kernel bitstreams and can (re)program the FPGA with the appropriate bitstream required from each application task. While spatial accelerator sharing enhances accelerator utilization and application response time compared to time-sharing, it does come at the expense of data isolation.

Finally, GPU spatial sharing lacks protection due to the single accelerator address space, leaving application data susceptible to exposure to other applications. Consequently, the feasibility of sharing in broad multi-user settings becomes compromised. To resolve this issue, we design and implement a software-based sandboxing approach that applies bitwise instructions in the virtual assembly code of kernels. Our approach does not require extra or specific hardware units and supports ML frameworks that use closed-source domainspecific libraries.

To minimize the porting effort of existing CUDA applications, we examine the interception of CUDA API calls at various levels, i.e., driver, runtime, and high-level library functions. We show that intercepting only the CUDA runtime and driver library is adequate to run complex ML frameworks, such as Caffe and PyTorch. Additionally, this level of interception is more robust than the ones used from previous approaches because it requires handling fewer and much simpler functions.

We use Caffe, TensorFlow, PyTorch, and Rodinia to demonstrate and evaluate the proposed runtime system in an accelerator-rich server environment using GPUs, FPGAs, and CPUs. Our results show that applications that use our system can safely share accelerators without any modifications at low overhead and with latency guarantees.

Keywords: Runtime System, Accelerators, Heterogeneity, Spatial Sharing, GPU Memory Protection, Preemption, Scheduling

> Supervisor: Angelos Bilas Professor

Computer Science Department University of Crete

### Περίληψη

Σήμερα, η αποτελεσματική χρήση πολλαπλών ετερογενών επιταχυντών σε εφαρμογές αλλά και σε δομές μηχανικής μάθησης (Machine Learning Frameworks) όπως το TensorFlow, το Py-Torch και το Caffe παρουσιάζει τέσσερις βασικές προκλήσεις: (α) Την κοινή χρήση ετερογενών επιταχυντών, (β) την ελαστική κατανομή των διαθέσιμων πόρων κατά την διάρκεια εκτέλεσης των εφαρμογών, (γ) την εξασφάλιση της απαιτούμενης απόδοσης σε εφαρμογές που η χρονική καθυστέρηση είναι σημαντική και (δ) την προστασία των δεδομένων των εφαρμογών που διαμοιράζονται ένα επιταχυντή.

Σε αυτή τη διατριβή, εισάγουμε ένα νέο σύστημα χρόνου εκτέλεσης που έχει σχεδιαστεί για να αποσυνδέει τις εφαρμογές από τις περιπλοκές διαδικασίες που απαιτούνται για την χρήση ετερογενών επιταχυντών. Η προσέγγισή μας περιλαμβάνει μια διεπαφή προγραμματισμού εφαρμογών (application programming interface) που χρησιμοποιείται από τις εφαρμογές και έτσι τους επιτρέπει να γράφονται μία φορά χωρίς να λαμβάνονται υπόψη λεπτομέρειες όπως ο αριθμός ή ο τύπος των επιταχυντών. Με τη χρήση του συστήματός μας, οι εφαρμογές απελευθερώνονται από την επιβάρυνση της επιλογής επιταχυντή, της δέσμευσης μνήμης και της διαχείρισης μνήμης. Όλες αυτές οι περίπλοκες διεργασίες διεκπεραιώνονται από μια υπηρεσία υποστήριξης – που αναφέρεται ως διακομιστής (server) – η οποία είναι κοινή και την διαμοιράζονται όλες οι εφαρμογές που εκτελούνται σε ένα κόμβο. Ο διακομιστής έχει τέσσερα βασικά χαρακτηριστικά.

Πρώτον, η ανάθεση μιας διεργασίας σε ένα επιταχυντή πραγματοποιείται την τελευταία στιγμή και όχι κατά την αρχικοποίηση της εφαρμογής όπως συμβαίνει με τις υπάρχουσες μεθόδους. Μετά την απόφαση ανάθεσης της διεργασίας και ακριβώς πριν από την εκτέλεση αυτής, ο διακομιστής μεταφέρει τα απαραίτητα δεδομένα στον επιλεγμένο επιταχυντή. Αυτή η δυναμική ανάθεση εργασιών και η καθυστερημένη τοποθέτηση δεδομένων επιτρέπουν την προσαρμογή στις αλλαγές φόρτου εφαρμογής.

Δεύτερον, για να διασφαλιστεί ο χρόνος απόχρισης σε συγχριμένες εφαρμογές όταν αυτές

διαμοιράζονται χρονικά μια κάρτα γραφικών, με άλλες που έχουν πυρήνες (kernels) που ο χρόνος εκτέλεσης τους είναι πολύ μεγάλος, ο διακομιστής μπορεί να σταματήσει την εκτέλεση αυτών των μεγάλων πυρήνων χρησιμοποιώντας ένα μηχανισμό ανάκλησης (revocation). Ο μηχανισμός ανάκλησής σταματά μια διεργασία τερματίζοντας πρόωρα τον πυρήνα που βρίσκεται σε εξέλιξη χωρίς να αποθηκεύει τα δεδομένα που χρησιμοποιεί και τον ξανά ξεκινάει αργότερα. Ο διακομιστής χρησιμοποιεί έναν προγραμματιστή χρόνου εκτέλεσης (scheduler) που δίνει προτεραιότητα σε κρίσιμες εφαρμογές έναντι άλλων χωρίς αυστηρές χρονικές απαιτήσεις και καθοδηγεί τον μηχανισμό ανάκλησης πότε πρέπει να σταματήσει ένα πυρήνα που εκτελείται.

Τρίτον, για να υποστηρίξει την χωρική διαμοίραση επιταχυντών μεταξύ εφαρμογών, ο διακομιστής δημιουργεί πολλαπλές ουρές εντολών σε κάθε επιταχυντή. Όσον αφορά τις FPGA, ο διακομιστής φορτώνει κυκλώματα (bit-streams) πολλαπλών πυρήνων και μπορεί να (επανα)προγραμματίσει την FPGA με το κατάλληλο bit-stream που απαιτείται για κάθε διεργασία. Ο χωρικός διαμοιρασμός επιταχυντών αυξάνει τη χρήση των πόρων του επιταχυντή και βελτιώνει τον χρόνο απόκρισης των εφαρμογών σε σχέση με τον χρονικό διαμοιρασμό, όμως εις βάρος της προστασίας των δεδομένων.

Η δυνατότητα που έχει μια εφαρμογή να διαβάσει και να γράψει τα δεδομένα μιας άλλης όταν χρησιμοποιούν ταυτόχρονα την ίδια κάρτα γραφικών κάνει τον χωρικό διαμοιρασμό αυτου του τύπου τον επιταχυντών σε περιβάλλοντα σύννεφου (cloud environments) που υπάρχουν πολλοί χρήστες να είναι απαγορευτική. Για να επιλύσουμε αυτό το ζήτημα, σχεδιάσαμε και εφαρμόσαμε μια τεχνική που εφαρμόζεται σε εικονική γλώσσα μηχανής (virtual assembly), δεν χρειάζεται παραπάνω ή ειδικές μονάδες υλικού (hardware units) και τέλος υποστηρίζει ML frameworks που χρησιμοποιούν κλειστές βιβλιοθήκες.

Για να ελαχιστοποιήσουμε την προσπάθεια μεταφοράς των υπαρχουσών CUDA εφαρμογών στην δικιά μας διεπαφή προγραμματισμού (API), εξετάζουμε την υποκλοπή κλήσεων του CUDA API σε διάφορα επίπεδα, δηλαδή το CUDA runtime, το CUDA driver, και κλήσεις σε υψηλού επιπέδου βιβλιοθήκες. Σε αυτήν την διατριβή δείξαμε ότι αν υποκλέψουμε μόνο τις CUDA runtime και CUDA driver βιβλιοθήκες είναι αρκετό για να τρέξουμε περίπλοκλα Machine Learning Frameworks. Επιπλέον αυτού του είδους η προσέγγισή είναι πιο αποδοτική σε σχέση με προηγούμενες διότι απαιτεί την διαχείριση λιγότερων κλήσεων.

Για να αξιολογήσουμε το σύστημα μας χρησιμοποιούμε πραγματικές εφαρμογές όπως τα

Caffe, TensorFlow, PyTorch και Rodinia. Επιπλέον χρησιμοποιήσαμε πολλαπλούς και διαφορετικούς τύπου επιταχυντές όπως GPUs, FPGAs, και CPUs. Τα αποτελέσματά μας δείχνουν ότι οι εφαρμογές που χρησιμοποιούν το σύστημά μας μπορούν με ασφάλεια να μοιράζονται πολλούς και διαφορετικού τύπου επιταχυντές χωρίς καμία τροποποίηση, με χαμηλό κόστος και με εγγυήσεις καθυστέρησης.

Λέξεις κλειδιά: Σύστημα Χρόνου Εκτέλεσης, Επιταχυντές, Ετερογένεια, Χωρικός διαμοιρασμός, Προστασία Μνήμης Επιταχυντών, Ανάκληση Εργασιών, Χρόνο-προγραμματισμός Διεργασιών

> Επόπτης: Άγγελος Μπίλας Καθηγητής Τμήμα Επιστήμης Υπολογιστών Πανεπιστήμιο Κρήτης

### **Bibliographic Notes**

The publications related to this dissertation (ordered by date) are:

- (i) Stelios Mavridis, Manos Pavlidakis, Ioannis Stamoulias, Christos Kozanitis, Nikos Chrysos, Christoforos Kachris, Dimitrios Soudris, and Angelos Bilas. 2017. *VineTalk: Simplifying software access and sharing of FPGAs in datacenters*. In Proceedings of the 27th International Conference on Field Programmable Logic and Applications (FPL '17).

- (ii) Manos Pavlidakis, Stelios Mavridis, Nikos Chrysos, and Angelos Bilas. 2020. TReM: A Task Revocation Mechanism for GPUs. In Proceedings of the 22th IEEE International Conference on High Performance Computing and Communications (HPCC '20).

- (iii) Manos Pavlidakis, Stelios Mavridis, Antony Chazapis, Giorgos Vasiliadis, and Angelos Bilas. Arax: A Runtime Framework for Decoupling Applications from Heterogeneous Accelerators. In Proceedings of the 13th ACM Symposium on Cloud Computing (SoCC '22).

- (iv) Manos Pavlidakis, Giorgos Vasiliadis, Stelios Mavridis, Antony Chazapis, and Angelos Bilas. *Guardian: Data Isolation for Multi-Tenant GPU Sharing*. (Under submission).

More specifically, Chapter 2 based on *(iii)*. Chapter 3 is based on *(i)*. Chapter 4 based on *(ii)*, and Chapter 5 on *(iv)*.

## Contents

| Acknowledgments                                |

|------------------------------------------------|

| Abstract                                       |

| Abstract in Greek                              |

| Bibliographic Notes                            |

| Table of Contents                              |

| List of Figures                                |

| List of Tables                                 |

| 1 Introduction                                 |

| 2 Decouple Applications and Accelerators       |

| 2.1 Design 9                                   |

| 2.1.1 Client                                   |

| 2.1.2 Server                                   |

| 2.1.3 Transport Layer                          |

| 2.1.4 Autotalk: stub-generator                 |

| 2.1.5 Implementation issues                    |

| 2.1.6 Implementing new applications using Arax |

| 2.2 Experimental Methodology 22                |

| 2.3 Experimental Evaluation                    |

| 2.3.1 Overhead of accelerator decoupling 24    |

| 2.3.2 Effectiveness of accelerator sharing     |

| 2.3.3 Performance gains of elasticity 30       |

| 2.3.4 Overhead of application migration        |

| 2.3.5 Overhead for Caffe and TensorFlow        |

| 2.4 Summary                                    |

| 3 | Simj | plify FP | GA Accessing & Sharing                                                     | 39 |

|---|------|----------|----------------------------------------------------------------------------|----|

|   | 3.1  | VineTa   | alk Design                                                                 | 40 |

|   |      | 3.1.1    | Software Facing API                                                        | 40 |

|   |      | 3.1.2    | Communication Layer                                                        | 41 |

|   |      | 3.1.3    | Software Controller                                                        | 42 |

|   |      | 3.1.4    | Hardware Facing API                                                        | 43 |

|   | 3.2  | Integr   | ation with SDAccel                                                         | 43 |

|   | 3.3  | Perfor   | mance Evaluation                                                           | 45 |

|   |      | 3.3.1    | Experimental Setup                                                         | 45 |

|   |      | 3.3.2    | VineTalk overhead                                                          | 46 |

|   |      | 3.3.3    | Accelerator time-sharing                                                   | 47 |

|   | 3.4  | Summ     | nary                                                                       | 48 |

| 4 | GPU  | J Kerne  | l Revocation                                                               | 49 |

|   | 4.1  | TReM     | revocation mechanism                                                       | 51 |

|   |      | 4.1.1    | Revoking a kernel with TReM                                                | 52 |

|   | 4.2  | Reduc    | ring SLA violations of user-facing tasks                                   | 55 |

|   |      | 4.2.1    | Elastic policy                                                             | 55 |

|   |      | 4.2.2    | Using TReM with Priority and Elastic                                       | 56 |

|   | 4.3  | Experi   | imental Methodology                                                        | 57 |

|   |      | 4.3.1    | Multi-GPU server configuration and memory affinity                         | 57 |

|   |      | 4.3.2    | Workloads                                                                  | 57 |

|   | 4.4  | Experi   | imental evaluation                                                         | 60 |

|   |      | 4.4.1    | Overhead of TReM revocation                                                | 60 |

|   |      | 4.4.2    | Effectiveness of TReM with long-running batch tasks $\ldots \ldots \ldots$ | 62 |

|   |      | 4.4.3    | Scalability of TReM                                                        | 65 |

|   | 4.5  | Discus   | ssion                                                                      | 67 |

|   | 4.6  | Summ     | nary                                                                       | 68 |

| 5 | Secu | ire GPU  | J Spatial Sharing                                                          | 69 |

|   | 5.1  | Introd   | luction                                                                    | 69 |

|   | 5.2  | Backg    | round                                                                      | 71 |

|   |      |          |                                                                            |    |

|   |      | 5.2.1  | GPU Programming Interfaces and Context                             |

|---|------|--------|--------------------------------------------------------------------|

|   |      | 5.2.2  | GPU Compilation Workflow                                           |

|   |      | 5.2.3  | GPU Memory Sharing Scope                                           |

|   |      | 5.2.4  | Addressing Modes                                                   |

|   | 5.3  | Threa  | t Model                                                            |

|   | 5.4  | Guard  | lian Design                                                        |

|   |      | 5.4.1  | Dynamically Loadable Library                                       |

|   |      | 5.4.2  | GPU manager                                                        |

|   |      | 5.4.3  | Offline Kernel Sandboxing                                          |

|   |      | 5.4.4  | Bounds Checking Tradeoffs 85                                       |

|   | 5.5  | Exper  | imental Methodology 87                                             |

|   | 5.6  | Exper  | imental Evaluation                                                 |

|   |      | 5.6.1  | Impact of Guardian at GPU Sharing                                  |

|   |      | 5.6.2  | Guardian Overheads Compared to Other Approaches Without Sharing 92 |

|   |      | 5.6.3  | Impact of Address Fencing on Register Usage                        |

|   |      | 5.6.4  | Performance of Address Fencing at High Cache Hit Ratio 95          |

|   |      | 5.6.5  | Performance of Guardian on Different GPUs and Access Patterns 96   |

|   |      | 5.6.6  | Cost of CUDA calls Interception                                    |

|   | 5.7  | Summ   | nary                                                               |

| 6 | Rela | ted Wo | rk                                                                 |

|   | 6.1  | Decou  | pling applications from accelerators                               |

|   | 6.2  | FPGA   | Software Access and Sharing 101                                    |

|   | 6.3  | GPU k  | xernel revocation and scheduling                                   |

|   |      | 6.3.1  | SLA-based scheduling                                               |

|   |      | 6.3.2  | State-saving preemption mechanisms                                 |

|   | 6.4  | GPU r  | nemory protection                                                  |

|   |      | 6.4.1  | Protect GPU Memory under GPU sharing                               |

|   |      | 6.4.2  | Detect Buffer Overflows for a Single Application                   |

|   |      | 6.4.3  | Ensure Privacy and Data Confidentiality                            |

|   |      | 6.4.4  | API Remoting                                                       |

| 7  | 7 Future Work |                                             |  |  |  |

|----|---------------|---------------------------------------------|--|--|--|

|    | 7.1           | Apply zero-copy in shared memory            |  |  |  |

|    | 7.2           | Use remote heterogeneous accelerators       |  |  |  |

|    | 7.3           | Batch dependent tasks 110                   |  |  |  |

|    | 7.4           | Compile PTX kernels to other GPUs           |  |  |  |

|    | 7.5           | Extend accelerator memory 111               |  |  |  |

|    | 7.6           | Integrate Arax to a cluster-level scheduler |  |  |  |

| 8  | Con           | clusions                                    |  |  |  |

| Bi | Bibliography  |                                             |  |  |  |

# **List of Figures**

| 2.1  | Arax high-level overview. The main components of Arax are: Clients, Server,    |    |

|------|--------------------------------------------------------------------------------|----|

|      | Transport layer, and Autotalk.                                                 | 9  |

| 2.2  | The steps required for an application migration. The task queue is marked      |    |

|      | orphan (1) and reassigned to a new thread (2). The relevant data are then      |    |

|      | transferred to the new accelerator via the server memory (3,4)                 | 12 |

| 2.3  | Arax dynamic task assignment. Application issues tasks to a task queue. Ini-   |    |

|      | tially, the task queue is assigned to an accelerator (1), then the accelerator |    |

|      | thread gets a task (2). It allocates accelerator memory for that data (3) and  |    |

|      | copies the data from the application (4)                                       | 15 |

| 2.4  | Client and Server stub generation (offline phase) and loading (online phase).  |    |

|      | The three steps of the offline phase are performed by the parser, the gener-   |    |

|      | ator, and the extractor.                                                       | 16 |

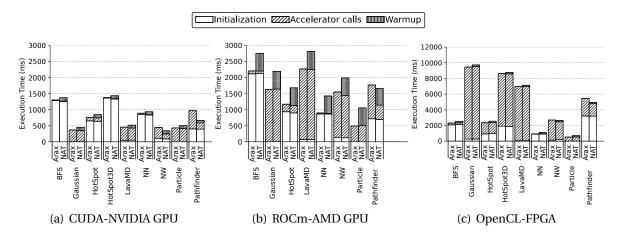

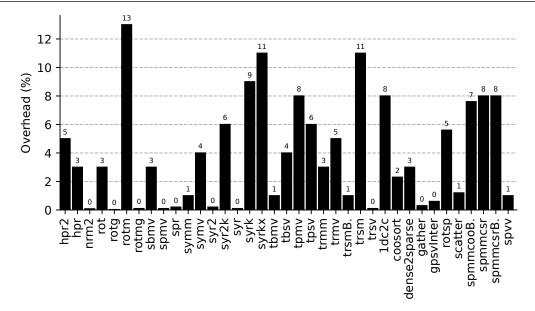

| 2.5  | Overhead of Arax compared to native (NAT) using Rodinia benchmarks over        |    |

|      | heterogeneous accelerators.                                                    | 25 |

| 2.6  | Breakdown of overhead for launching an empty kernel with Arax (CPU cycles).    | 26 |

| 2.7  | Execution time normalized to native for Arax and AvA                           | 27 |

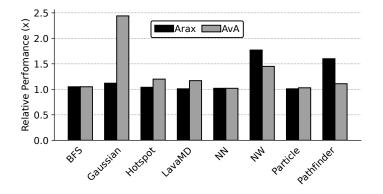

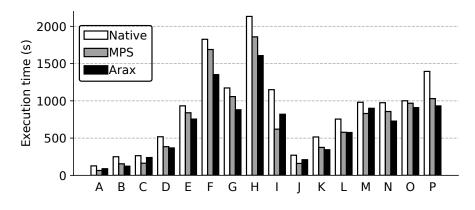

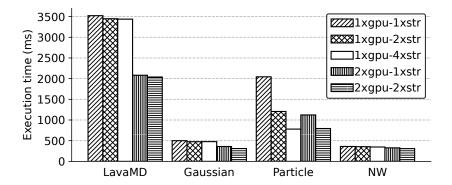

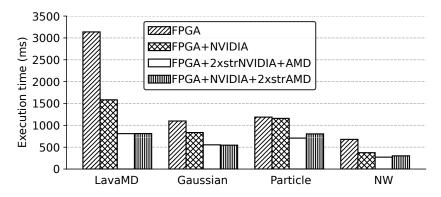

| 2.8  | Effectiveness of sharing with NVIDIA GPUs for Arax, native (without MPS),      |    |

|      | and MPS                                                                        | 28 |

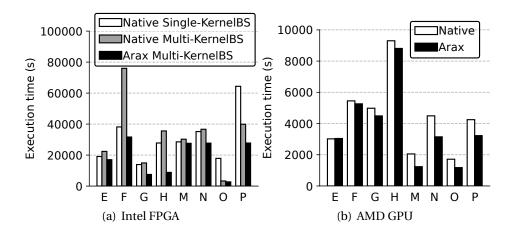

| 2.9  | Effectiveness of sharing with Intel FPGAs and AMD GPUs for Arax and Na-        |    |

|      | tive. For FPGAs we compare Arax with a multi-kernel & a single-kernel bit-     |    |

|      | stream.                                                                        | 29 |

| 2.10 | Performance improvement of applications when increasing the number of          |    |

|      | homogeneous accelerators or GPU streams.                                       | 31 |

|      |                                                                                |    |

| 2.11 | Performance improvement of applications when increasing the number of          |    |

|------|--------------------------------------------------------------------------------|----|

|      | heterogeneous accelerators or GPU streams.                                     | 32 |

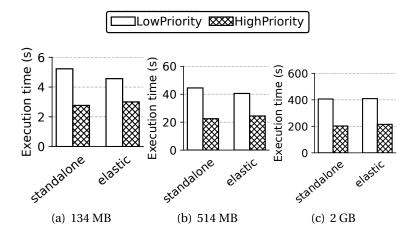

| 2.12 | Effectiveness of migration when decreasing the accelerators provided to a      |    |

|      | low-priority application upon the arrival of a high-priority one. We compare   |    |

|      | elasticity with the standalone execution in which applications are statically  |    |

|      | assigned to accelerators. We use datasets from 134 MB up to 2 GB               | 33 |

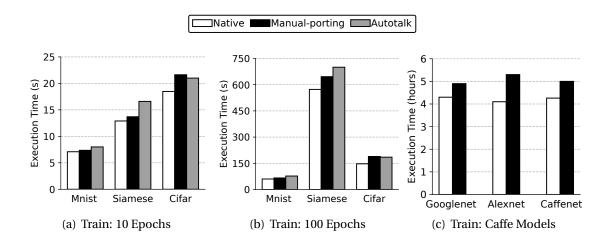

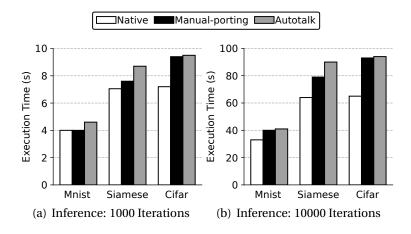

| 2.13 | The overheads of Arax using manual-porting and Autotalk (automatic stub        |    |

|      | generation) compared to native CUDA for Caffe using ML <i>training</i>         | 35 |

| 2.14 | The overheads of Arax using manual-porting and Autotalk (automatic stub        |    |

|      | generation) compared to native CUDA for Caffe using ML <i>inference</i>        | 36 |

| 3.1  | Design overview of VineTalk. VA represent VineAccelerator (described in        |    |

|      | Section 3.1.2)                                                                 | 40 |

| 3.2  | Buffer transfers necessary for an inout argument over VineTalk, SDAccel/CUDA   | A, |

|      | sockets protocols/APIs.                                                        | 42 |

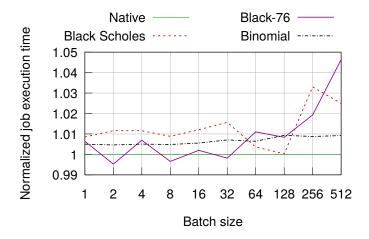

| 3.3  | VineTalk integration with SDAccel.                                             | 44 |

| 3.4  | Performance comparison between VineTalk-applications, and their stan-          |    |

|      | dalone execution over SDAccel. The x-axis is the stock batch size, the y-axis  |    |

|      | is the normalized job execution time in msec.                                  | 45 |

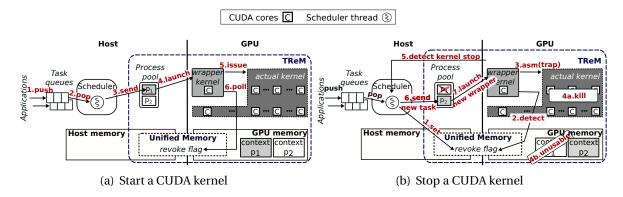

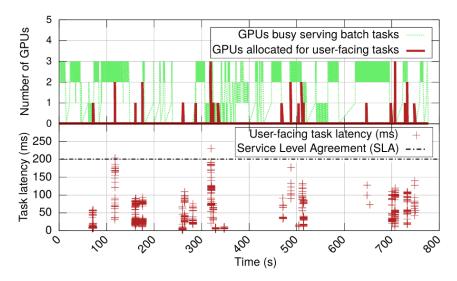

| 4.1  | TReM overview. The scheduler is part of the Arax server                        | 51 |

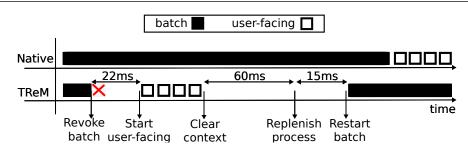

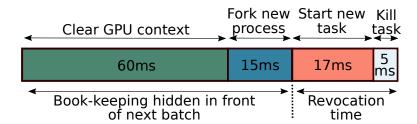

| 4.2  | The timing of TReM compared to native execution. Batch execution time is       |    |

|      | in the range of seconds                                                        | 54 |

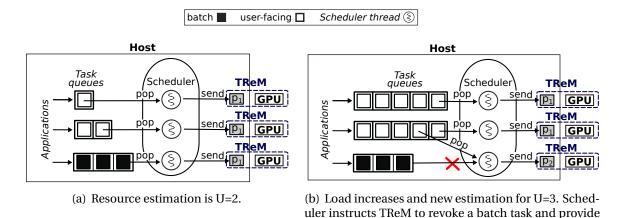

| 4.3  | TReM + Elastic in multi-GPU setups.                                            | 54 |

| 4.4  | TReM overhead breakdown.                                                       | 60 |

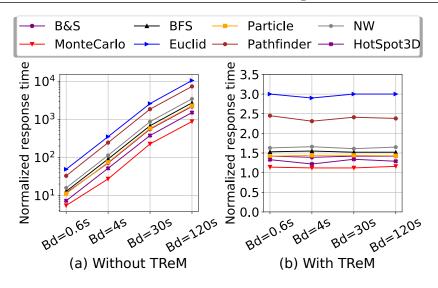

| 4.5  | Normalized response time of user-facing tasks over their stand-alone exe-      |    |

|      | cution in the presence of batch tasks with different duration (Bd). $\ldots$ . | 62 |

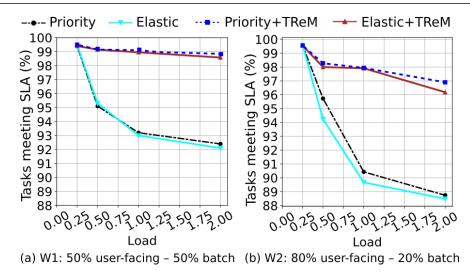

| 4.6  | Percentage of tasks that meet their SLA (y-axis) at increasing GPU load (x-    |    |

|      | axis), for workloads W1 (left) and W2 (right)                                  | 63 |

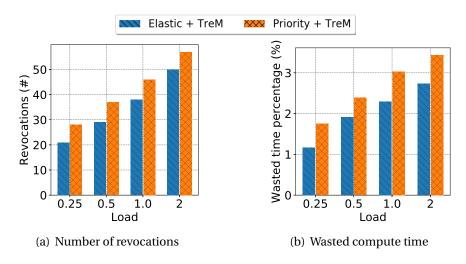

| 4.7  | Revocations overhead: (a) Number of task revocations; (b) Wasted compute       |    |

|      | time due to revocations.                                                       | 64 |

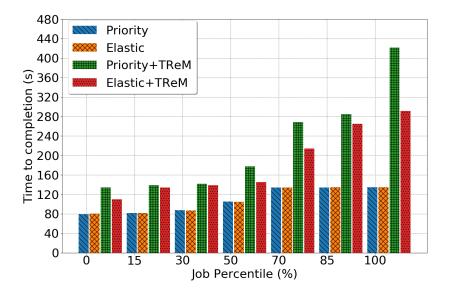

| 4.8  | Time to completion for batch jobs under different scheduling policies, for          |    |

|------|-------------------------------------------------------------------------------------|----|

|      | load 2.0                                                                            | 65 |

| 4.9  | Dynamic GPU allocation in Elastic and impact on SLA violations.                     | 66 |

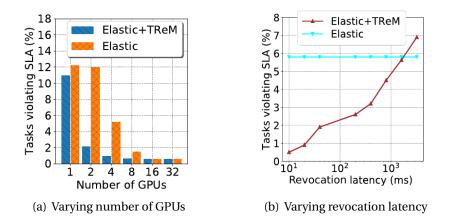

| 4.10 | SLA violations for W1 and W2 under load 1.0; (a) varying the number of              |    |

|      | GPUs (revocation latency 22ms); (b) varying the revocation latency (4 GPUs).        | 67 |

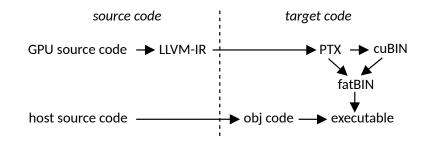

| 5.1  | Compilation flow of CUDA applications.                                              | 73 |

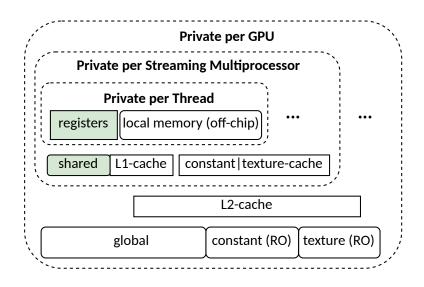

| 5.2  | NVIDIA GPU memory hierarchy and sharing scope.                                      | 74 |

| 5.3  | Multi-tenant spatial GPU sharing, without Guardian. The common GPU                  |    |

|      | context required for spatial sharing allows applications to access each oth-        |    |

|      | ers memory.                                                                         | 77 |

| 5.4  | Guardian online and offline (dashed annotated) mechanisms to allow pro-             |    |

|      | tected spatial GPU sharing. Guardian intercepts the CUDA runtime inter-             |    |

|      | face used from applications and perform the necessary checks at memory              |    |

|      | allocations, transfers, and kernel executions. This allows kernels from dif-        |    |

|      | ferent applications to execute concurrently on different memory partitions,         |    |

|      | eliminating illegal accesses.                                                       | 78 |

| 5.5  | Guardian CUDA library interception level versus previous approaches [24,            |    |

|      | 23, 28, 98]. Guardian intercepts only the CUDA runtime and driver APIs and          |    |

|      | <i>not</i> the high-level calls to CUDA accelerated libraries as in previous works. | 80 |

| 5.6  | Bitwise instructions mask addresses that fall outside a partition.                  | 84 |

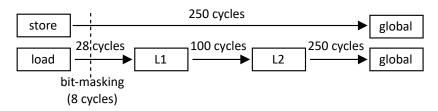

| 5.7  | Bit-masking latency (8-cycles) compared to latency of different memories.           | 86 |

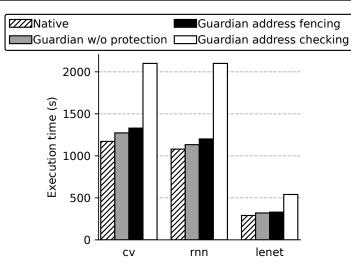

| 5.8  | GPU sharing using native CUDA time sharing (protected), MPS spatial shar-           |    |

|      | ing (unprotected), Guardian spatial sharing without protection, and Guardian        |    |

|      | spatial sharing with address fencing under workloads with the <b>same</b> appli-    |    |

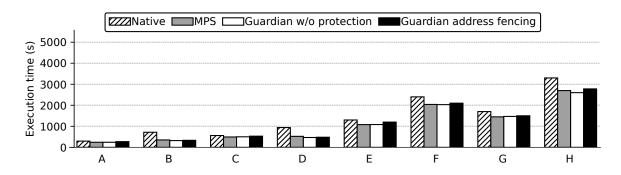

|      | cations.                                                                            | 91 |

| 5.9  | GPU sharing using native CUDA time sharing (protected), MPS spatial shar-           |    |

|      | ing (unprotected), Guardian spatial sharing without protection, and Guardian        |    |

|      | spatial sharing with address fencing under workloads with the different ap-         |    |

|      | plications.                                                                         | 91 |

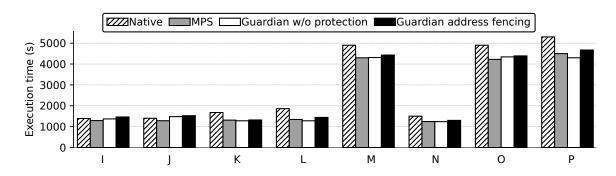

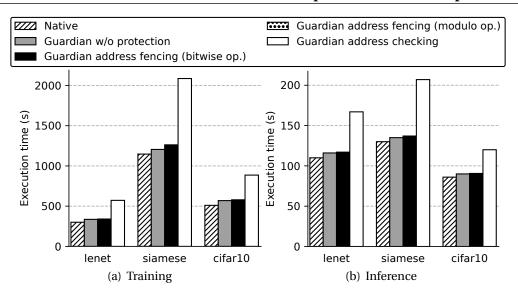

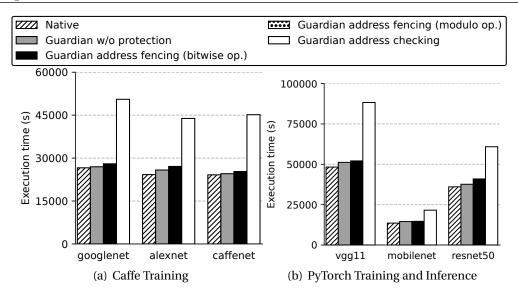

| 5.10 | Comparison of address fencing (bitwise) with other approaches, using Caffe      |     |

|------|---------------------------------------------------------------------------------|-----|

|      | with <i>mnist and cifar</i> dataset                                             | 92  |

| 5.11 | Comparison of address fencing (bitwise) with other approaches, using Caffe      |     |

|      | and PyTorch with the <i>imagenet</i> dataset                                    | 93  |

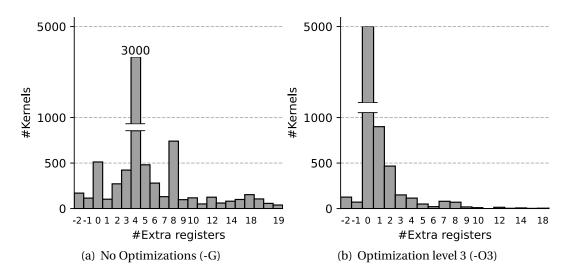

| 5.12 | Guardian's per thread register usage vs native                                  | 94  |

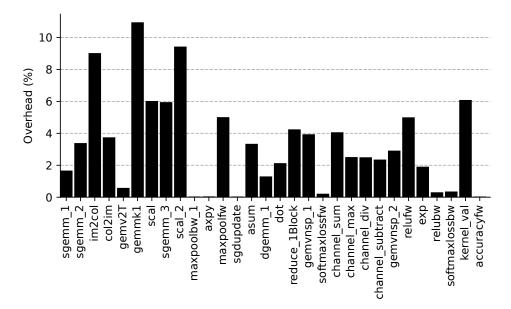

| 5.13 | Performance overhead of sandboxed kernels against native execution              | 95  |

| 5.14 | Guardian overhead with PyTorch and Caffe on GeForce GPU, compared to            |     |

|      | native execution.                                                               | 96  |

| 5.15 | Guardian overhead (%) for 37 kernels from CUDA-accelerated libraries com-       |     |

|      | pared to native execution of each kernel on the GeForce GPU                     | 97  |

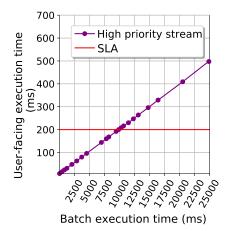

| 6.1  | Evaluating NVIDIA compute preemption by collocating two tasks in the same       |     |

|      | GPU using high- and low-priority streams. The user-facing task is assigned      |     |

|      | to the high-priority stream and a batch to the low-priority one. The high-      |     |

|      | priority stream preempts the low-priority one. As we increase the batch du-     |     |

|      | ration (x-axis), the duration of the user-facing task is affected and increases |     |

|      | linearly.                                                                       | 104 |

## **List of Tables**

| 2.1 | Methods of Arax API.                                                       | 11 |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Servers configurations.                                                    | 22 |

| 2.3 | Applications and their memory footprint.                                   | 22 |

| 2.4 | Workloads for spatial sharing.                                             | 24 |

| 2.5 | The execution time (seconds) of Caffe when the execution is migrated from  |    |

|     | the NVIDIA GPU to another accelerator. CPU only and NVIDIA only repre-     |    |

|     | sent the native execution without migrations.                              | 35 |

| 2.6 | The execution time (seconds) of TensorFlow and Keras for Autotalk and na-  |    |

|     | tive CUDA                                                                  | 37 |

| 3.1 | Main methods of the Software-facing API and comparison with Arax client-   |    |

|     | side API                                                                   | 41 |

| 3.2 | Overall application execution time (seconds) and Overhead (%) with 2000    |    |

|     | options and batch sizes 1 and 512.                                         | 47 |

| 3.3 | Comparison of the job execution time of 1 and 2 concurrent VineTalk appli- |    |

|     | cation(s) with applications running directly on the FPGA (i.e. Native)     | 47 |

| 4.1 | Latency of different methods to revoke/preempt a kernel running on a GPU.  | 51 |

| 4.2 | Average task execution time (ms)                                           | 58 |

| 4.3 | Workload configurations.                                                   | 59 |

| 5.1 | cuBIN and PTX kernel code included in CUDA-accelerated libraries for dif-  |    |

| 5.1 |                                                                            |    |

|     | ferent CUDA versions and GPUs.                                             | 74 |

| 5.2 | GPU specifications we use for the evaluation.                              | 87 |

| 5.3 | Load and store instructions in CUDA-accelerated libraries and frameworks |     |

|-----|--------------------------------------------------------------------------|-----|

|     | we use.                                                                  | 88  |

| 5.4 | Mixes of workloads used for assessing the performance of Guardian under  |     |

|     | GPU sharing                                                              | 89  |

| 5.5 | Guardian average cost in CPU cycles for the main operations performed    |     |

|     | when a kernel launch is intercepted and replaced with a sandboxed kernel | 98  |

| 6.1 | Capabilities of Arax vs. state-of-the-art approaches.                    | 100 |

| 6.2 | TReM and prior state-of-the-art approaches.                              | 105 |

| 6.3 | Comparing Guardian with state-of-the-art memory protection approaches    |     |

|     | for GPU sharing                                                          | 107 |

# Chapter 1 Introduction

The increasing need for high performance at low energy consumption has resulted in the proliferation of heterogeneous accelerators, such as GPUs, FPGAs, and TPUs [29, 26, 5, 96, 99, 85]. Recent estimates [85, 5, 11, 100, 113] indicate that servers will include a plethora of processing units and specialized accelerators [15, 19, 58, 92]. This trend poses significant challenges in how applications and higher-level frameworks, such as TensorFlow [1], PyTorch [78], and Caffe [41], can fully utilize the capacity of heterogeneous accelerators.

Today, a large percentage of applications or frameworks is *statically bound to specific accelerators throughout their execution*. In particular, many applications are directly written for one accelerator type, e.g., NVIDIA GPUs, to allow for device-specific optimizations. Over the last years, unified programming models, e.g., SYCL [84] and oneAPI [3], aim to offer portability to different accelerator types. However, applications are still required to explicitly select the desired accelerators during initialization and prior to starting their execution. As a result, each application execution is statically bound to a specific set of accelerators or types that cannot change at runtime. This results in poor resource and application efficiency in two ways: (a) reduced sharing of resources and (b) lack of adaptation over time.

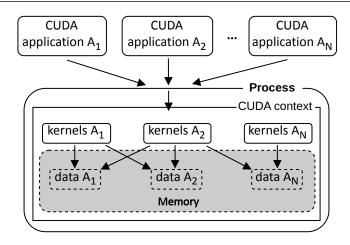

Existing resource assignment techniques fully allocate accelerators to a single application. Although practical, this exclusive assignment creates significant *load imbalance* in heterogeneous setups with multiple accelerators and results in resource under-utilization. Time-sharing approaches [108, 109, 113, 35, 63] cannot address this issue effectively because accelerators become "beefier" and individual applications and, even more so, individual kernels often fail to fully utilize all the available accelerator resources [113, 20, 69, 54, 8, 74, 115]. To address these limitations, several research approaches propose spatial sharing mechanisms [110, 20, 115, 31, 104, 112, 103, 57]. However, existing approaches are limited to specific accelerator types and require applications to perform manual task assignment and data placement. Regarding GPUs, NVIDIA offers Multiple Process Service (MPS), which allows different CUDA applications to execute concurrently in the same GPU. MPS offers a single GPU context, i.e., a common accelerator address space, that is a requirement for NVIDIA GPUs to allow kernels from different applications (and users) to execute concurrently. AMD GPUs offer by default this shared context, avoiding the need for such a service. However, this single/shared context introduces a significant concern: GPU kernels execute in the same GPU address space, hence they can modify (either inadvertently or deliberately) memory locations that belong to other applications [21, 76, 81, 65, 53, 51, 8] leading to confidentiality and integrity violations. This lack of memory protection makes spatial sharing impractical for generic multi-user environments.

Applications often exhibit dynamic behavior and fluctuating load requirements [35, 108]. Current approaches assign resources to each application that remain fixed throughout its execution. Assigning resources statically to applications is challenging due to the difficulty in accurately estimating their resource demands prior to execution. The lack of *dynamic task assignment* and *data-migration* results in application under- or overprovisioning and eventually to poor resource utilization. Existing approaches [35, 108] can dynamically assign whole *applications* to NVIDIA GPUs –not individual tasks– while their migration mechanisms rely either on domain-specific application features (TensorFlow checkpoints) or vendor-specific accelerator mechanisms (unified memory). Apart from application load, GPU workloads also have a dynamic behavior. Consequently, a GPU preemption mechanism is required to provide low latency in high-priority tasks in the presence of long-running batch tasks. A preemption mechanism consists of three parts; (1) stop the currently executing task, (2) save its state, and (3) replay the task later. Previous works [106, 68, 116] do not provide a bounded latency due to their "task stop" and state-saving mechanisms. Therefore, high-priority tasks still incur high tail latencies.

This dissertation proposes a runtime system that decouples applications from heterogeneous accelerators within a single server. Our approach is based on RPC, a mechanism that is proven to be very successful in decoupling complex software stacks, using clear and conceptually simple boundaries. We offer a client-side API that allows applications to be written once without considering any low-level details, such as the number or type of accelerators. Applications that use our system do not need to perform accelerator selection, memory allocations, or memory management operations. All these operations are handled transparently by a backend service, the server. The server is common and shared from all applications and offers four main features.

(1) Our server assigns a task to an accelerator (NVIDIA GPU, AMD GPU, FPGA) or a CPU as late as possible, differently from existing approaches that assign an *application* to an accelerator during its initialization (Arax § 2). After the task assignment and just before the task execution, the server transfers the required data to the selected accelerator. This dynamic task assignment and the lazy data placement enable adaptation to application load changes.

(2) To ensure that latency-critical applications will have the desired performance when they time-share a GPU, the server revokes the execution of long-running kernels. Our revocation mechanism stops a GPU task by aborting its currently executing GPU kernel without saving any state and replays it later (TReM § 4). The server uses a runtime scheduler that prioritizes latency-critical tasks over batch and instructs the revocation mechanism when to kill a running kernel.

(3) To enable spatial accelerator sharing across applications, the server creates multiple streams for GPUs and command queues for FPGAs (Arax § 2). Regarding FPGAs, it loads multi-kernel bitstreams and can (re)program the FPGA with the appropriate bitstream required from each application task (VineTalk § 3). Spatial accelerator sharing improves accelerator utilization and application turnaround time.

(4) Spatial sharing offered by our system and also from previous works [110, 20, 115, 31, 104, 112] does not offer protection for applications that share a GPU. Consequently, application data are exposed to other applications, making sharing impractical for generic

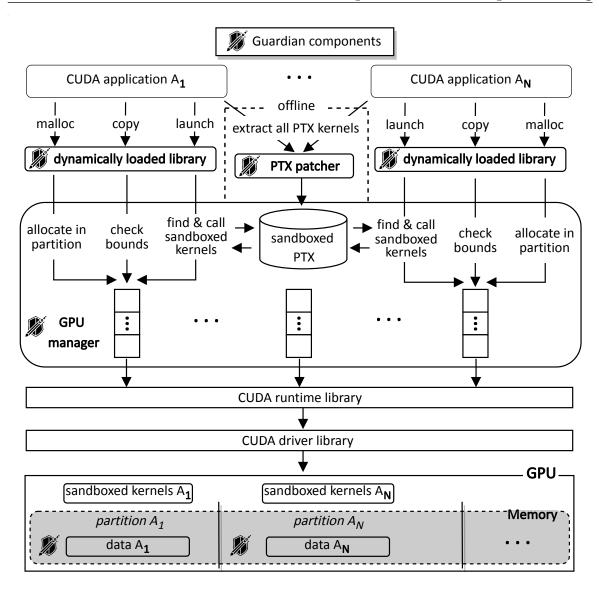

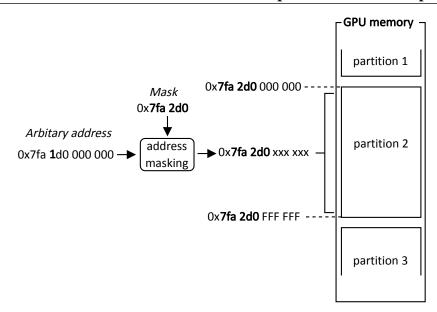

multi-user environments. To resolve this issue, we design and implement a PTX-based sandboxing approach to isolate data for applications that spatially share a GPU (Guardian § 5).

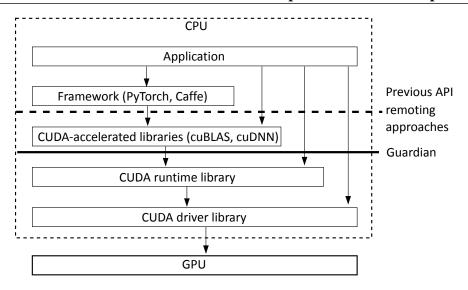

(5) Application porting to our *agnostic* client-side API requires manual effort, which is prohibitive in complex frameworks. To reduce the porting effort, we design and implement an automatic stub generator in Arax (§ 2) that ports a CUDA application to our client API. We focus on CUDA since NVIDIA GPUs dominate the accelerator market, and thus, complex frameworks such as Caffe, PyTorch, and TensorFlow can run to heterogeneous accelerators. The only requirement that our tool has is the existence of the kernels for the different accelerator types. Our approach intercepts the CUDA runtime (e.g., cudaMalloc(), cudaLaunchKernel()), the CUDA driver (e.g., cuMemAlloc(), cudnActivation-Forward()). Due to the complexity of this approach due to the interception of more than 1600 high-level calls that are complex and change rapidly in Guardian (§ 5) we move our interception one level deeper and intercept only the CUDA runtime and driver libraries. Although challenging because we need to handle an undocumented call (i.e., cudaGetExportTable()), it is proved to be more robust.

**Thesis statement:** Provide transparent and efficient sharing of heterogeneous accelerators for real-world applications in a server.

#### Contributions

The specific contributions of this dissertation are:

- 1. We remove static application to accelerator assignment that affects utilization using a generic client-side API and a backend service. The client-side API abstracts accelerator type and number, whereas the service manages multiple and heterogeneous accelerators in a server.

- 2. To reduce the programming effort required to port existing applications to our clientside API, we investigate the interception of CUDA API calls at various levels, i.e., driver, runtime, and high-level library functions calls. We concluded that the ap-

propriate level of interception is the CUDA runtime API.

- 3. Our backend service improves accelerator utilization and adapts to the fluctuating load requirements using six main mechanisms that can be applied to different accelerator types (i.e., NVIDIA GPUs, AMD GPUs, and FPGAs): spatial sharing, elasticity, dynamic task assignment, lazy data placement, live-migration, and task revocation.

- 4. Spatial GPU sharing imposes confidentiality and integrity violations. As a result, we examine the memory protection of kernels running concurrently on NVIDIA GPUs and provide a transparent memory protection mechanism. Our mechanism applies address fencing instructions before every load and store in the PTX-level of CUDA kernels.

#### Organization

The rest of this dissertation is organized as follows. Chapter 2 presents Arax the runtime used to decouple ML applications from heterogeneous accelerators. Chapter 3 explains in detail VineTalk, which includes the mechanisms that simplify the use of FPGAs and FPGA sharing. Chapter 4 shows the kernel revocation mechanism and the scheduling policies required to ensure the Service Level Agreement (SLA) for latency-critical applications when they time-share a GPU, named TReM. Chapter 5 presents Guardian a mechanism that enables protected GPU spatial sharing. Chapter 6 reviews related work and compares our approach with existing systems. Chapter 7 outlines prospective directions for future work, and chapter 8 concludes this thesis.

# Chapter 2 Decouple Applications and Accelerators

This chapter shows how to avoid static application to accelerator assignment that leads to underutilization. To achieve that, we propose an RPC-based approach that decouples applications from heterogeneous accelerators *within* a single server, named Arax. The client-side stubs of Arax allow applications to be written once using a simple API without considering any low-level details, such as the number or type of accelerators. Additionally, Arax applications do not need to perform accelerator selection, memory allocation, or task assignment operations; all are handled transparently by a backend service, the Arax server. Our server assigns applications tasks dynamically (not at application initialization) and performs memory allocations-transfers lazily and only after a task is assigned to a specific accelerator. To improve accelerator utilization while ensuring application performance Arax provides three capabilities:

(a) **Spatial sharing** that manages existing mechanisms in heterogeneous accelerators, transparently, and across all applications in a server. We use asynchronous host-threads to issue tasks to GPU streams and FPGA command queues. Regarding FPGAs, Arax loads bit-streams with multiple kernels that need to be collocated in the same FPGA. The advantage of our approach is that it moves all the related management from individual applications to the shared Arax runtime and can make decisions across all applications.

(b) **Elasticity and dynamic resource assignment** to applications at runtime. To achieve this, Arax requires fine-grain access to application tasks and their data. Arax uses asynchronous operations to issue independent tasks across different accelerators, while en-

suring that tasks with dependencies execute in-order.

(c) **Live-migration** that moves application tasks across heterogeneous accelerators. Unlike existing approaches, our migration mechanism does not require application modifications or specialized accelerator support. Arax uses task arguments to keep track of the data used by each task and transfers only relevant data upon task migration. Although arbitrary pointers may result in moving large amounts of memory, our approach is adequate to support real applications, such as TensorFlow and Caffe.

Finally, Arax includes **Autotalk**, a generator that creates stubs for a given accelerator API based on a description of the target API provided by the user once. Applications are then linked dynamically with the stub library that internally calls the Arax API. Currently, Autotalk generates stubs for a subset of CUDA that can support Caffe and TensorFlow.

We evaluate Arax using Caffe, TensorFlow, and Rodinia. Our results show that Arax applications can run without any modifications at low overhead—up to 12% compared to native—when other approaches, i.e., AvA [113], result in up to 30% overhead for the same applications running on a GPU. In addition, Arax provides elasticity, decreasing total application turnaround time by 2× compared to native execution without elasticity support. Our migration mechanism adds 7% overhead compared to standalone execution. Finally, our sharing mechanism provides up to 20% improvement in total execution time compared to NVIDIA MPS.

The specific contributions of this chapter are:

- 1. We propose an RPC-based approach to decouple applications from heterogeneous accelerators within servers.

- 2. We present a mechanism for spatial sharing of heterogeneous accelerators and dynamic and transparent assignment of tasks to accelerators.

- 3. We present an application live-migration mechanism that reduces data movement based on data ownership by tasks.

- 4. We present a stub generator that allows existing applications to use Arax with minimal effort and demonstrate our approach with Caffe and TensorFlow.

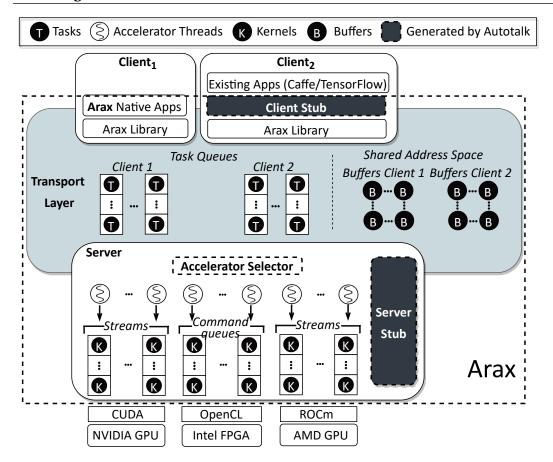

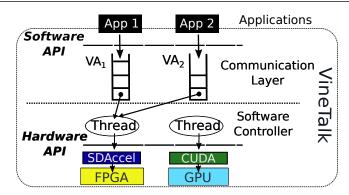

Figure 2.1: Arax high-level overview. The main components of Arax are: Clients, Server, Transport layer, and Autotalk.

5. We demonstrate and evaluate Arax in an accelerator-rich server environment, using GPUs, FPGAs, and CPUs, with Caffe, TensorFlow, and Rodinia.

# 2.1 Design

Figure 2.1 shows a high-level overview of Arax. Applications use the Arax API to access available accelerators, regardless of their types. Applications create task queues and issue tasks, providing their data in the form of Arax buffers. Tasks and buffers are being transported to the Arax server via a transport layer over shared memory, mapped to both the application and server address spaces. The Arax server assigns dynamically and asynchronously application tasks to accelerators, managing accelerator streams and command

queues, maintaining task ordering, and handling data dependencies. Finally, Arax's stub generator, Autotalk, allows generating the stub library automatically for a particular accelerator API, given a description file of the API calls. Next, we discuss each component of Arax in more detail.

### 2.1.1 Client

Arax provides three basic abstractions to hide accelerator types and number from applications: (a) *tasks*, (b) *task buffers*, and (c) *task queues*. Table 2.1 shows an overview of the main Arax API calls.

**Tasks**: A task can be either a compute or a transfer task and is used to hide acceleratorspecific information. A compute task is an accelerator kernel, while a transfer task is a data transfer between the host and the accelerator and vice versa. Both tasks are executed without interruption and are asynchronous. Arax provides synchronization primitives to allow applications to wait for their completion. A compute task takes the kernel name and its corresponding arguments as parameters, i.e., inputs, outputs, and arguments required from a kernel. The kernel name is associated with the actual kernel at the server (§2.1.2). Unlike existing accelerator APIs, task arguments do not include accelerator-specific information, such as thread number or thread size. The parameters for a transfer task include the task buffers provided by Arax and any data from the application address space.

**Task buffers:** A buffer is an opaque identifier that represents the input and output data of a task and is used to hide accelerator memory. Multiple tasks or applications can operate on the same buffer concurrently. It is important to note that Arax decouples the accelerator memory management from applications using a lazy memory allocation strategy. When an application requests memory, Arax stores the requested allocation size but does not allocate this memory on the accelerator (§2.1.2). The actual allocation will be performed only after the task is successfully assigned to an accelerator. In the meantime, applications can continue issuing tasks since buffers are implemented as opaque types in the shared memory. For all allocations in the shared memory, we use the Doug Lea allocator. This abstraction hides accelerator memory, and applications are unaware of which

#### 2.1. Design

| Abstraction | API call                   | Description                   |  |

|-------------|----------------------------|-------------------------------|--|

| Tasks       | a_issue()                  | Issue a task                  |  |

| 14585       | a_wait()                   | Wait for a task               |  |

|             | a_allocate()               | Allocate Buffer               |  |

| Buffers     | a_free()                   | Free Buffer                   |  |

|             | a_sync_to(), a_sync_from() | Transfer Data                 |  |

| Tack Queros | a_acquire()                | Acquire a virtual accelerator |  |

| Task Queues | a_release()                | Release a virtual accelerator |  |

Table 2.1: Methods of Arax API.

accelerator hosts their data.

**Task queues:** Applications issue tasks to task queues, similar to existing programming models, e.g., CUDA/ROCm streams and OpenCL command queues. The main difference of Arax is that these queues are not assigned directly to an accelerator. Instead, Arax is responsible for assigning them to one or more accelerators at runtime (§2.1.2), while ensuring that asynchronous tasks will be executed in-order. Each task queue holds tasks with dependencies. To denote independent sets of work, applications need to acquire different task queues. This approach works well for the ML frameworks we examine due to the inherent serialization of NN layers.

#### 2.1.2 Server

The Arax server is responsible for maintaining task issue order and managing data dependencies while performing dynamic task assignment and data placement to accelerators. These mechanisms allow Arax to provide efficient spatial sharing and elastic allocation of resources.

**Spatial Sharing:** The spatial sharing mechanism of Arax is based on streams/command queues and host-threads (Arax accelerator threads). In particular, to execute kernels in parallel, the server spawns multiple threads per physical accelerator. Each accelerator thread internally creates different streams (CUDA and ROCm) or command queues (OpenCL). The design of spatial sharing in Arax can support advanced task assignment policies that do not rely on low-level accelerator-specific APIs. To enable spatial sharing for NVIDIA GPUs, we require a single context; thus, the Arax server is implemented as

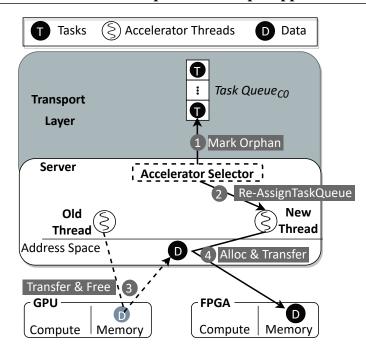

Figure 2.2: The steps required for an application migration. The task queue is marked orphan (1) and reassigned to a new thread (2). The relevant data are then transferred to the new accelerator via the server memory (3,4).

a single process for all accelerators. Regarding FPGAs, the Arax server loads a bitstream that contains multiple kernels, similar to Vinetalk [63]. The server can select and load the appropriate bitstream to serve each task.

**Application migration:** Even when accelerators are shared, there can be load imbalances. Arax offers an application migration mechanism to correct load imbalances. This migration mechanism can move application tasks and their data across heterogeneous accelerators. The migration mechanism cannot stop a task during execution. Instead, it waits for the task to finish and moves any pending tasks and their data to another accelerator. There are *three challenges* that our migration mechanism needs to tackle:

(*i*) *Migrate an application without interrupting its execution*. Arax offers task queues to applications to issue their tasks. The Arax server stops and resumes the execution of a task queue, and thus it does not affect the execution of the application. In particular, Arax performs the following steps: (a) The server marks this task queue as an orphan (Figure 2.2; step **1**). At this point, accelerator threads cannot launch tasks from this task queue. (b)

#### 2.1. Design

Since then, there could have been tasks issued for execution; the server waits for them to finish before re-assigning this task queue to a different accelerator thread (Figure 2.2; step 2). (c) From here on, any remaining task from this particular task queue will be invoked to the new accelerator. We note that, during the migration, the application continues issuing tasks to its task queues.

(*ii*) Move only the data of the migrated task. The server should move only the data required from the migrated task and not all the application state. Existing checkpoint approaches [108, 16] migrate all the application state, which involves transfers in the range of gigabytes. The Arax server maintains metadata for each task and is aware of the data required. After assigning the task queue to a new accelerator thread, the server instructs the previous accelerator thread to copy the task data from its accelerator memory to the server memory and free the corresponding allocations (Figure 2.2; step (3)). The server then notifies the new accelerator thread to allocate and copy that data from the server's memory (Figure 2.2; step (3)) using the native accelerator API. We note that the server memory is an intermediate buffer to transfer data across different accelerators. As part of our future work, we plan to eliminate this extra copy using accelerator-to-accelerator transfers, at least for the cases supported [86].

*(iii) Migrate the most recent version of the data.* Before a data migration, we must ensure that the data required from the migrated task(s) are up-to-date. To achieve that, the server allows only one valid copy of the data (at any given time) to the distinct accelerator memories in multi-accelerator setups.

**Dynamic task assignment:** The server assigns the incoming task queues to the underlying accelerators. Individual tasks from the same task queue can be assigned to different accelerators. This assignment involves task and data migrations for tasks with dependencies. When the server detects an unassigned, non-empty task queue, it assigns it to an accelerator using a round-robin policy (default). Advanced assignment policies can be implemented with relatively low effort. This is facilitated by the fact that Arax already collects information regarding the memory footprint of each task, the number of tasks per accelerator, and the data ownership.

As a proof of concept that our accelerator selector can host advanced assignment poli-

cies, we also implement an elastic assignment policy. This policy is essential to handle load fluctuations or data bursts by performing dynamic task assignments. The server keeps track of the assigned task queues per accelerator and knows the owner of each task queue. Consequently, the accelerator selector can increase/decrease the accelerators assigned to an application based on the load.

For instance, lets assume that we have a low-priority application with two task queues, i.e., *task queue1* and *task queue2*. Initially, both task queues are assigned to the same accelerator. When the accelerator selector detects idle accelerators, it expands the resources used by the low-priority application by assigning *task queue2* to the idle accelerator. Reversely, when another high-priority application arrives, the server shrinks the accelerators used from the low-priority application by moving *task queue2* to the accelerator where *task queue1* executes. This re-assignment requires moving the application state between accelerators, i.e., application migration. Consequently, the high-priority application can make exclusive use of the idle accelerator.

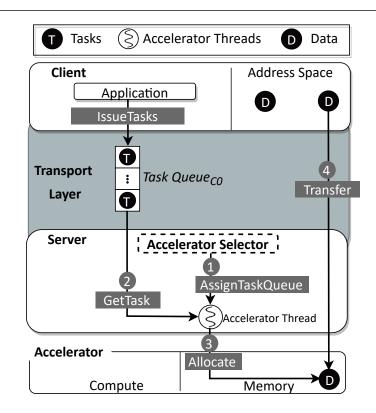

To perform memory management, the server maintains internally a mapping of the allocated buffers per task queue and their corresponding sizes. We note that the actual memory allocation is performed only after its corresponding task queue has been assigned to a physical accelerator (Figure 2.3; step **1**). After the selection of the physical accelerator, the thread of that accelerator gets a task from the task queue (Figure 2.3; step **2**) and checks if any memory has already been allocated in that particular accelerator memory. If not, it performs the actual allocation (Figure 2.3; step **3**) and keeps a reference to that memory segment so that it can be used for deallocation purposes. After that, the accelerator thread can issue the task to the accelerator. If the task is a data transfer, the accelerator thread copies the data from the client address space to the accelerator memory (Figure 2.3; step **4**).

To support different accelerator types, the server spawns separate accelerator threads. Each thread uses the accelerator's native API to communicate with that particular accelerator. Currently, Arax supports NVIDIA GPUs using CUDA, Intel Altera FPGAs using OpenCL, and AMD GPUs using ROCm. When receiving a compute task, the accelerator thread uses the kernel name—passed as a task parameter—to find the appropriate kernel

#### 2.1. Design

Figure 2.3: Arax dynamic task assignment. Application issues tasks to a task queue. Initially, the task queue is assigned to an accelerator (1), then the accelerator thread gets a task (2). It allocates accelerator memory for that data (3) and copies the data from the application (4).

program and loads it to the physical accelerator for execution. For this reason, the server maintains a dispatch table that associates kernel names with the actual kernel programs in the server stub.

We assume that kernels are implemented by third-party experts using the native accelerator's API. Accelerators offer libraries such as RAND (Random Number Generation) and BLAS (Basic Linear Algebra Subroutine). The function calls in these libraries can involve multiple kernel invocations internally, which cannot be extracted in case the library is closed-source (e.g., NVIDIA cuBLAS and cuRAND). To overcome this limitation, we incorporate these libraries into Arax, as-is, forming different server stubs, one for each accelerator. The server stubs are compiled using the accelerator-specific compilers. For NVIDIA GPUs we use NVCC, for Intel FPGAs we use AOCL, and for AMD GPUs we use HIPCC.

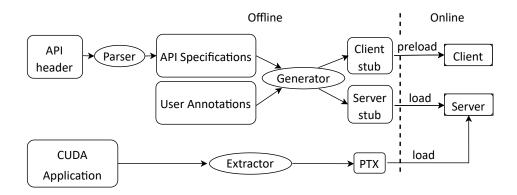

Figure 2.4: Client and Server stub generation (offline phase) and loading (online phase). The three steps of the offline phase are performed by the parser, the generator, and the extractor.

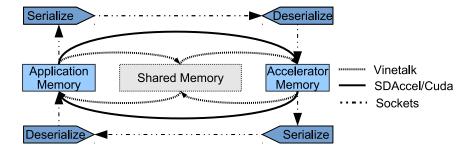

#### 2.1.3 Transport Layer

Arax applications and the Arax server are separate processes. Consequently, Arax requires an IPC mechanism for the applications and the server to exchange tasks and data. We use a shared memory approach to avoid system calls in the common path. Our initial implementation of the shared memory transport layer uses an extra copy of the data. In particular, application data are copied in the shared memory segment. Then, the server copies the data to the accelerator memory. We evaluate the impact of this copy in Section 2.3.1. We believe that future versions of Arax should consider zero-copy mechanisms by using shared pointers between the application and server address spaces.

#### 2.1.4 Autotalk: stub-generator

Existing frameworks are complex and require considerable manual effort to port them to different accelerator APIs. Arax reduces this effort by providing Autotalk, a generator implemented as a python script that creates client and server stubs for each accelerator API offline (Figure 2.4; Offline). The generated stubs are linked with the applications and the Arax server during their initialization (Figure 2.4; Online). The offline phase is performed once and consists of three main steps: *parse, generate,* and *extract.*

Step 1: Parse. The Autotalk parser gets as input an accelerator API header and produces

an API specification file (Figure 2.4; API specifications). The specification file contains for each API call, the number of arguments, their order, and the return value. The current version of Autotalk targets the CUDA API (v10.1) and can automatically create the API specification file for 85% of the existing functions (1800 in total) without requiring any user intervention.

**Step 2: Generate.** The Autotalk generator takes as input the API specification file that has been produced from the parser and an annotation file provided by the user (Figure 2.4; User Annotations). This user-provided annotation file contains information about the function calls that cannot be auto-produced from the Autotalk parser and require manual effort. The parser fails for some API calls because they take pointers as parameters, the bounds of which cannot be generated automatically in C/C++, and the address space they belong to (host or device), cannot be found automatically. The user annotation file provides this information with size expressions that calculate the bounds of each pointer. It also specifies the address space of the pointer parameter based on each API's documentation. The user annotation file is created once and consists of 2-3 lines of code for each function that cannot be generated automatically. Currently, these functions are about 270 (out of the 1800 in CUDA API v10.1). The generator produces the client and server stubs using the API specification and the user annotation files. The client stub contains an implementation of the accelerator API used by applications over the Arax API. The server stub contains the function calls to accelerator libraries (e.g., BLAS, RAND).

**Step 3: Extract.** Autotalk uses cuobjdump [65, 95] to extract kernels from the native CUDA applications that are not included in accelerator libraries (Figure 2.4; Extractor); these kernels are in PTX format [71] and are dynamically linked with the server executable so they can be invoked at runtime.

#### 2.1.5 Implementation issues

The current version of Arax supports the execution of kernels on CPU and three accelerator types: NVIDIA GPUs, AMD GPUs, and Intel Altera FPGAs. To add a new accelerator, one should implement an new accelerator thread that will contain the following functions: accelAlloc() and accelFree() that are responsible for memory allocations and de-allocations respectively; accelSyncTo() and accelSyncFrom() that transfer data to and from the accelerator; accelMemset() that sets device memory to a particular value and accelDevcpy() that performs a transfer within an accelerator. These functions are implemented once for each accelerator type using the native accelerator API.

Accelerator APIs offer function calls that query specific device information, such as cudaGetDeviceProperties(), and cudaGetDeviceCount(). The design of Arax hides the number and type of the underlying accelerators, so it cannot provide such information. Instead, the Arax server returns some "synthesized" information, ensuring that calls depending on such information will run correctly. This information is based on the specifications of the accelerator with minimal resources; by doing so, we ensure that an application will execute to at least one accelerator. We note that this approach is acceptable for the applications used in our experimental evaluation; however, other applications may require advanced policies, which is left as future work.

Existing applications can use library handles or generators, such as cuBLAS handles or cuRAND generators. Typically, library handles and generators are opaque structures that store the context required from a library. However, these handles do not have the same semantics in all accelerator libraries. For instance, CBLAS (the BLAS library for CPUs) does not have the notion of handles. Such cases are managed by Arax before issuing a task to an accelerator: The accelerator threads that are implemented using the native accelerator API prepare handles and generators according to the semantics of each accelerator and use them during the kernel invocation.

## 2.1.6 Implementing new applications using Arax

In this section, we describe how we port a gaussian from Rodinia benchmark suite to Arax API as an example to write new applications to Arax. To port gaussian to Arax we use the CUDA version (Listing 2.1) and replace all CUDA calls (i.e. allocations, transfers, and kernel calls) with the relevant Arax API calls, as shown in Listing 2.2. In particular a *cudaMalloc()* is replaced with *a\_allocate()*, *cudaMemcpy(HostToDevice)*, *cudaMem*-

*cpyAsync(HostToDevice)*, and *cudaMemcpy(DeviceToHost)* with *a\_sync\_to()* and *a\_sync\_from()* respectively. Regarding calls that set or copy data to the device, such as *cudaMemset* and *cudaMemcpy(DeviceToDevice)* we issue a task to the server that will call the appropriate function. Moreover, we replace *cudaLaunchKernel()* with *a\_issue()*. When the kernel call is synchronous we use *a\_task\_wait()*.

```

void ForwardSub() {

int t;

float *m_cuda, *a_cuda, *b_cuda;

// allocate memory on GPU

cudaMalloc((void **)&m_cuda, Size * Size * sizeof(float));

cudaMalloc((void **)&a_cuda, Size * Size * sizeof(float));

cudaMalloc((void **)&b_cuda, Size * sizeof(float));

// copy memory to GPU

cudaMemcpy(m_cuda, m, Size * Size * sizeof(float), cudaMemcpyHostToDevice);

cudaMemcpy(a_cuda, a, Size * Size * sizeof(float), cudaMemcpyHostToDevice);

cudaMemcpy(b_cuda, b, Size * sizeof(float), cudaMemcpyHostToDevice);

int block_size, grid_size;

block_size = MAXBLOCKSIZE;

grid_size = (Size / block_size) + (!(Size % block_size) ? 0 : 1);

dim3 dimBlock(block_size);

dim3 dimGrid(grid_size);

int blockSize2d, gridSize2d;

blockSize2d = BLOCK_SIZE_XY;

gridSize2d = (Size / blockSize2d) + (!(Size % blockSize2d ? 0 : 1));

dim3 dimBlockXY(blockSize2d, blockSize2d);

dim3 dimGridXY(gridSize2d, gridSize2d);

for (t = 0; t < (Size - 1); t++) \{

Fan1<<<dimGrid, dimBlock>>>(m_cuda, a_cuda, Size, t);

Fan2<<<dimGridXY, dimBlockXY>>>(m_cuda, a_cuda, b_cuda, Size, Size - t, t);

}

// copy memory back to CPU

cudaMemcpy(m, m_cuda, Size * Size * sizeof(float), cudaMemcpyDeviceToHost);

cudaMemcpy(a, a_cuda, Size * Size * sizeof(float), cudaMemcpyDeviceToHost);

cudaMemcpy(b, b_cuda, Size * sizeof(float), cudaMemcpyDeviceToHost);

```

```

cudaFree(m_cuda);

cudaFree(a_cuda);

cudaFree(b_cuda);

```

}

Listing 2.1: guassian implementation with CUDA API.

```

void ForwardSub() {

a_accel *accel;

gaussianArgs gArgs;

a_task *t_fan1, *t_fan2;

std::vector<a_task *> free_v;

free_v.reserve(128);

a_buffer_s a_fan1;

// input

// output

a_buffer_s m_fan1;

a_buffer_s inputs_fan2[2]; // inputs fan2

a_buffer_s b_fan2;

// input and output for fan2

// Set the accelerator type.

a_accel_type_e accelType = ANY;

// Create a task for each kernel.

a_proc *fan1 = a_proc_get("fan1");

a_proc *fan2 = a_proc_get("fan2");

accel = a_accel_acquire_type(accelType);

// Allocate memory

m_fan1 = (a_buffer_s *)a_allocate(

vpipe, Size * Size * sizeof(float), 64); // output fan1

a_fan1 = (a_buffer_s *)a_allocate(

vpipe, Size * Size * sizeof(float), 64); // input fan1

b_fan2 =

(a_buffer_s *)a_allocate(vpipe, Size * sizeof(float), 64);

// Transfer data

a_sync_to(m_fan1, accel, m);

a_sync_to(a_fan1, accel, a);

a_sync_to(b_fan2, accel, b);

inputs_fan2[0] = m_fan1;

inputs_fan2[1] = a_fan1; // in to fan2

```

```

gArgs.size = Size;

// Issue task to accelerator (block, grid size are calculated in the server).

for (int t = 0; t < (Size - 1); t++) {

gArgs.t = t;

t_fan1 = a_issue(accel, fan1, &gArgs, sizeof(gaussianArgs), 1,

&a_fan1, 1, &m_fan1);

free_v.push_back(t_fan1);

t_fan2 = a_issue(accel, fan2, &gArgs, sizeof(gaussianArgs), 2,

inputs_fan2, 1, &b_fan2);

free_v.push_back(t_fan2);

}

a_sync_from(a_fan1, a);

a_sync_from(m_fan1, m);

a_sync_from(b_fan2, b);

for (auto &i : free_v) {

a_task_free(i);

}

a_free(m_fan1);

a_free(a_fan1);

a_free(b_fan2);

a_accel_release(&accel);

```

```

Listing 2.2: guassian implementation with Arax API.

```

# 2.2 Experimental Methodology

}

For our evaluation, we use two servers with different accelerator types, as shown in Table 2.2. The first server (S1) is equipped with one FPGA and two different GPUs, while the second (S2) with two identical NVIDIA GPUs. The NVIDIA RTX 4000 is equipped with 8 GB of GDDR6, has 2304 CUDA cores, and is connected over PCIe v3 x16. The NVIDIA RTX 2080 Ti has 11 GB GDDR6, consists of 4352 CUDA cores, and uses a PCIe v3 x8 port in our server. For the NVIDIA GPUs, we use CUDA v10.1. The Intel Arria 10 FPGA (de5a\_net\_ddr4) has 4 GB of DDR4 and uses PCIe v3 x8. We use OpenCL 1.2 and Quartus 20.1 to implement and compile the bitstreams and the server accelerator threads. AMD RX550X GPU has 512 compute cores, has 4 GB of GDDR5 VRAM, and uses PCIe v3 x16. For the AMD GPU, we

| ID | СРИ                                         | RAM<br>(GB) | PCIe<br>Gen | Accelerators                                                                    |

|----|---------------------------------------------|-------------|-------------|---------------------------------------------------------------------------------|

| 1  | AMD EPYC 7551P 64-Core<br>@ 3.0GHz          | 128         | 3.0         | (i) NVIDIA RTX 4000,<br>(ii) Intel Altera Arria 10 FPGA<br>(iii) AMD RX550X GPU |

| 2  | Intel Xeon CPU E5-2620 16-Core<br>@ 2.10GHz | 256         | 3.0         | 2x NVIDIA Geforce<br>RTX 2080                                                   |

| Suite<br>/ Framework | Application                    | Input Data<br>(MB) | Output Data<br>(MB) | Kernel<br>code |

|----------------------|--------------------------------|--------------------|---------------------|----------------|

|                      | BFS                            | 40                 | 4                   |                |

|                      | Gaussian (2k)                  | 32                 | 32                  |                |

|                      | Gaussian (1k)                  | 8                  | 8                   |                |

|                      | Hotspot                        | 8                  | 4                   | CUDA           |

| Rodinia              | Hotspot3D                      | 16                 | 8                   |                |

| Rouinia              | LavaMD                         | 60                 | 25                  | ROCm           |

|                      | NN                             | 16                 | 8                   | OpenCL         |

|                      | NW                             | 512                | 256                 |                |

|                      | Particle                       | 1.5                | 0.25                |                |

|                      | Pathfinder                     | 1024               | 0.6                 |                |

|                      | Mnist                          | 284                | 279                 |                |

| Caffe                | Siamese                        | 566                | 556                 |                |

|                      | Cifar                          | 1052               | 1050                | CUDA           |

|                      | Googlenet                      | 3416               | 3400                | ROCm           |

|                      | Alexnet                        | 5472               | 5470                |                |

|                      | Caffenet                       | 4274               | 4274                |                |

| TF                   | Mnist                          | 5460               | 5460                | CUDA           |

|                      | Computer Vision (CV)           | 3316               | 3216                |                |